IC DESIGN VERIFICATION

IC設計驗證服務

針對IC製作前,提供專業的設計規則檢查(DRC)和電路佈局驗證(LVS)服務,確保IC設計符合製造要求,避免晶片故障,提高設計品質和可靠性。

DRC

設計規則檢查

LVS

佈局驗證

品質

可靠性

IC

驗證

設計規則檢查 DRC

Design Rule CheckingDRC是確保設計符合製造要求,並避免晶片故障的重要步驟。它確保設計與製程技術的限制相符,並有助於提高設計的品質和可靠性。檢查晶片元件的間距、尺寸、金屬線寬、接合區域等。

製造要求

製程限制

品質保證

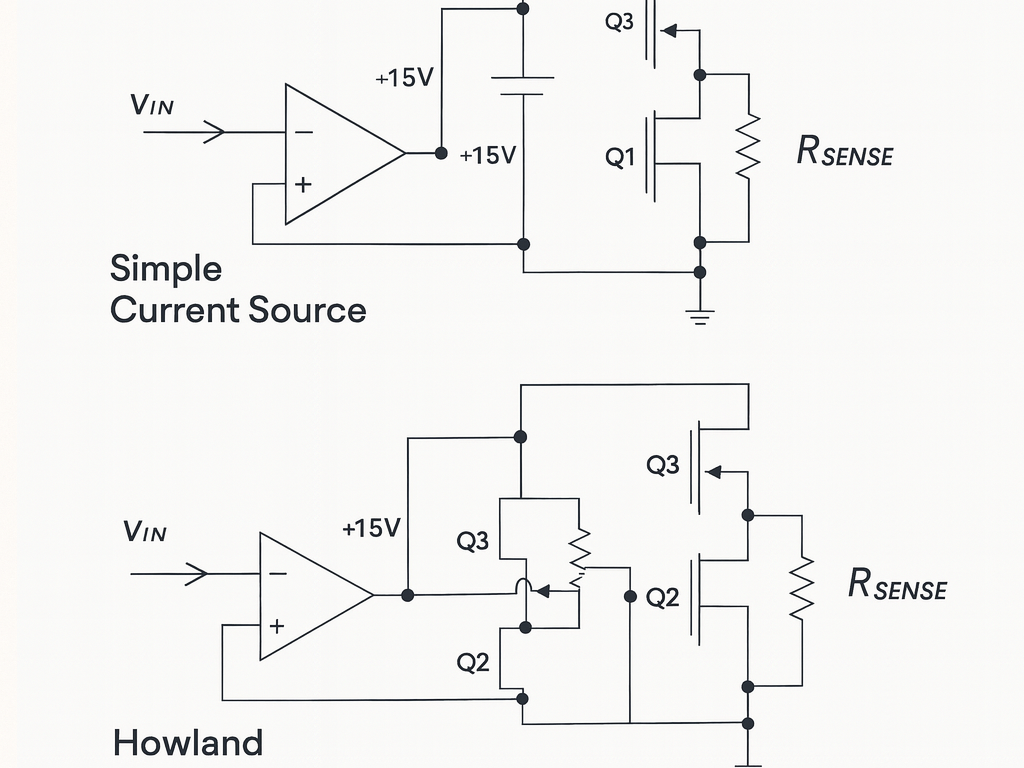

電路佈局驗證 LVS

Layout Versus SchematicLVS驗證確保了佈局的準確性和一致性,幫助設計師確保設計的可靠性和性能。它也有助於減少後續製程製造的風險,提高產品的可靠性和成功率。驗證原理圖與佈局的一致性。

佈局驗證

一致性檢查

可靠性

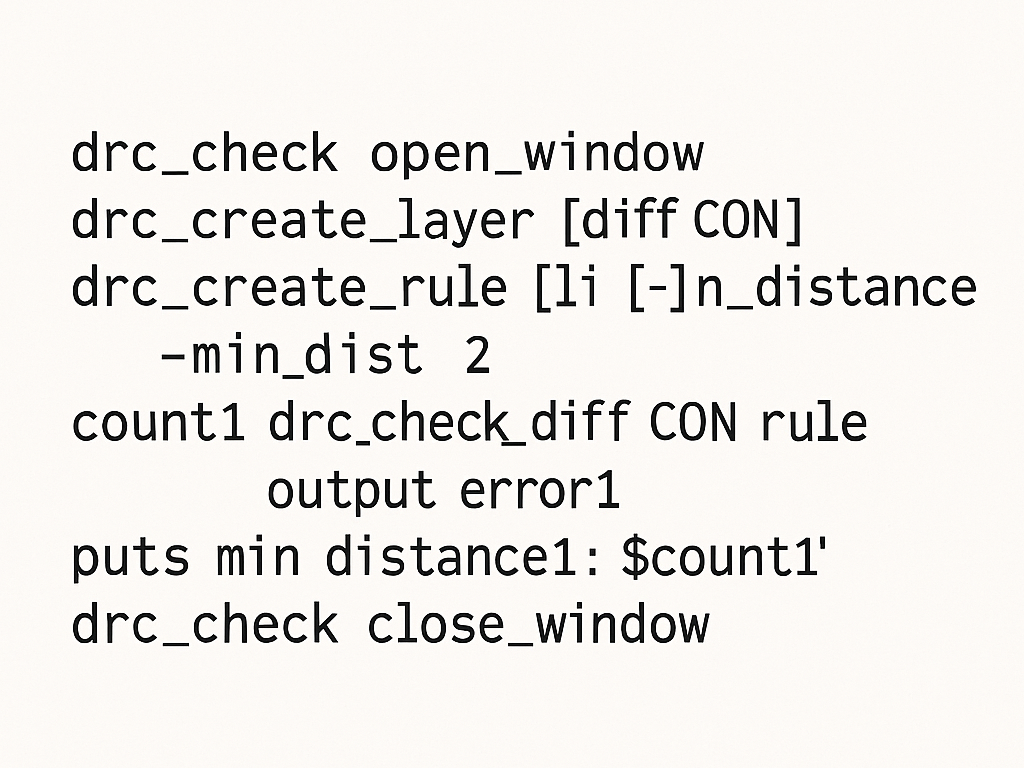

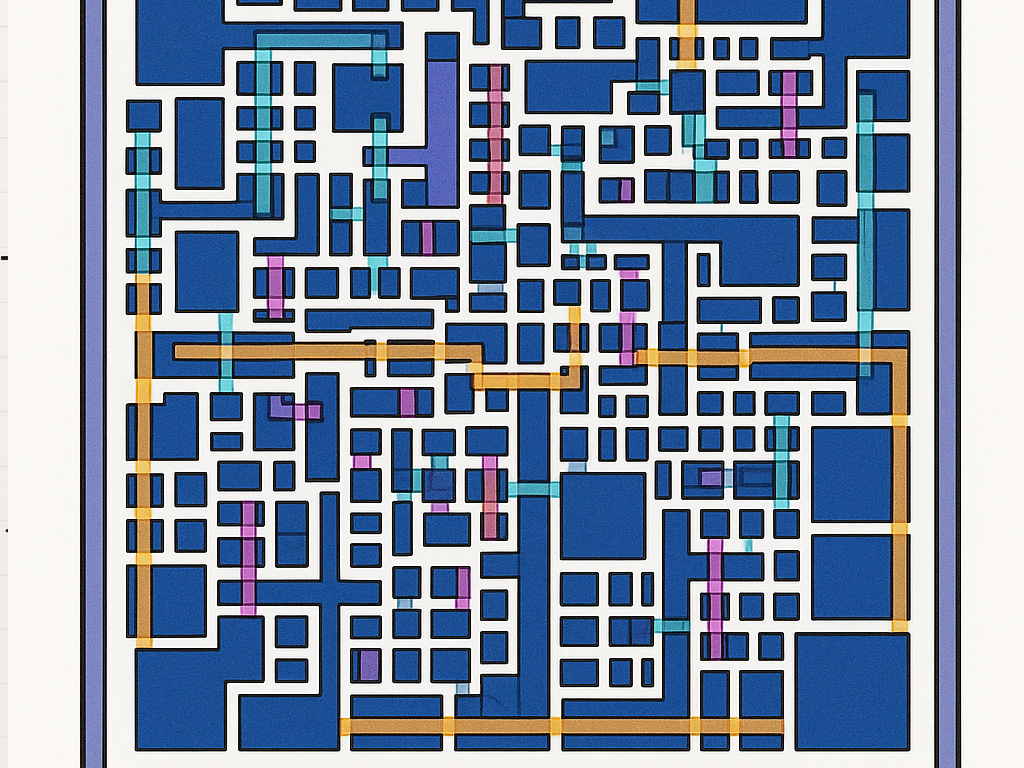

DESIGN RULE CHECKING

設計規則檢查 DRC

確保設計符合製造要求,避免晶片故障的重要步驟。

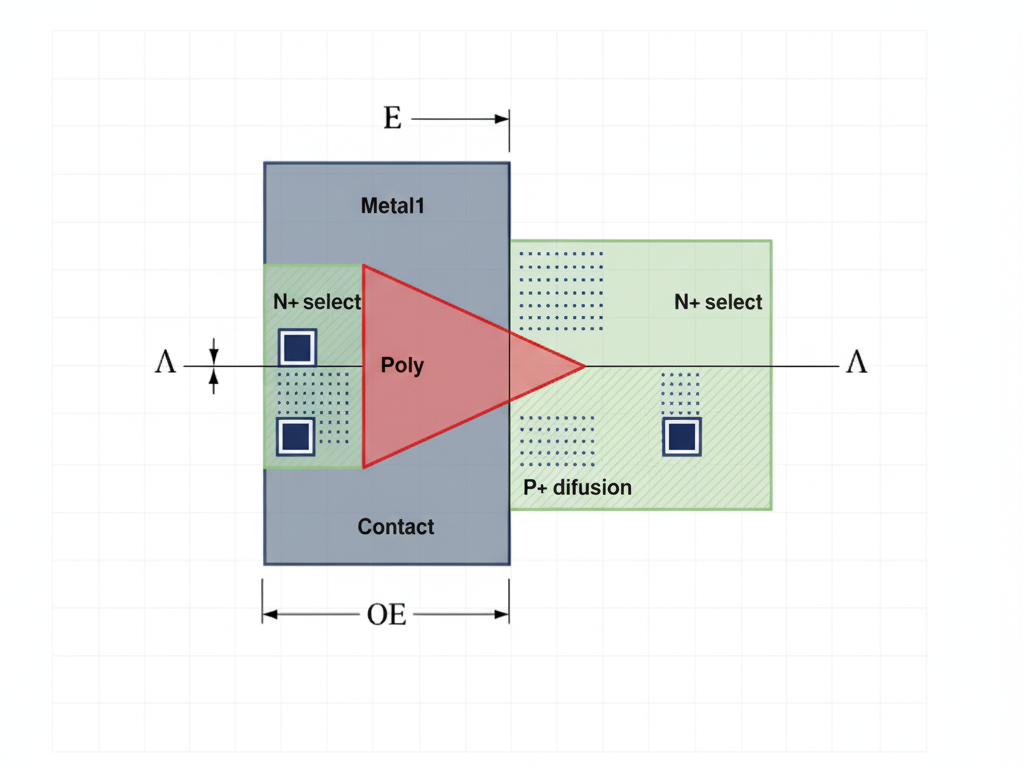

DRC是一個軟體工具,使用製程技術所設定的規則來檢查設計佈局的合規性。這些規則可以包括晶片元件的間距、尺寸、金屬線寬、接合區域等等。

檢查項目:

尺寸檢查

檢查元件的寬度、長度是否符合製程要求

間距檢查

檢查元件彼此之間的距離是否符合規範

電壓分級檢查

高電壓與低電壓元件的分開檢查

非法圖形檢查

避免客戶劃出非法的CMOS結構圖形

DRC

檢查

LVS

驗證

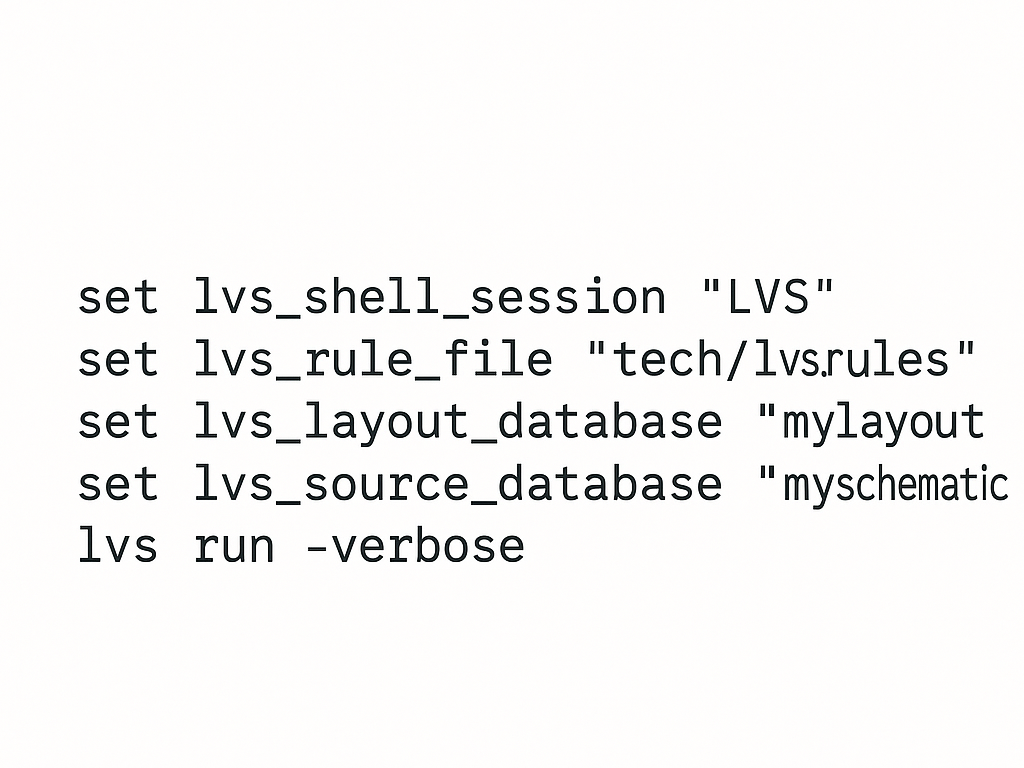

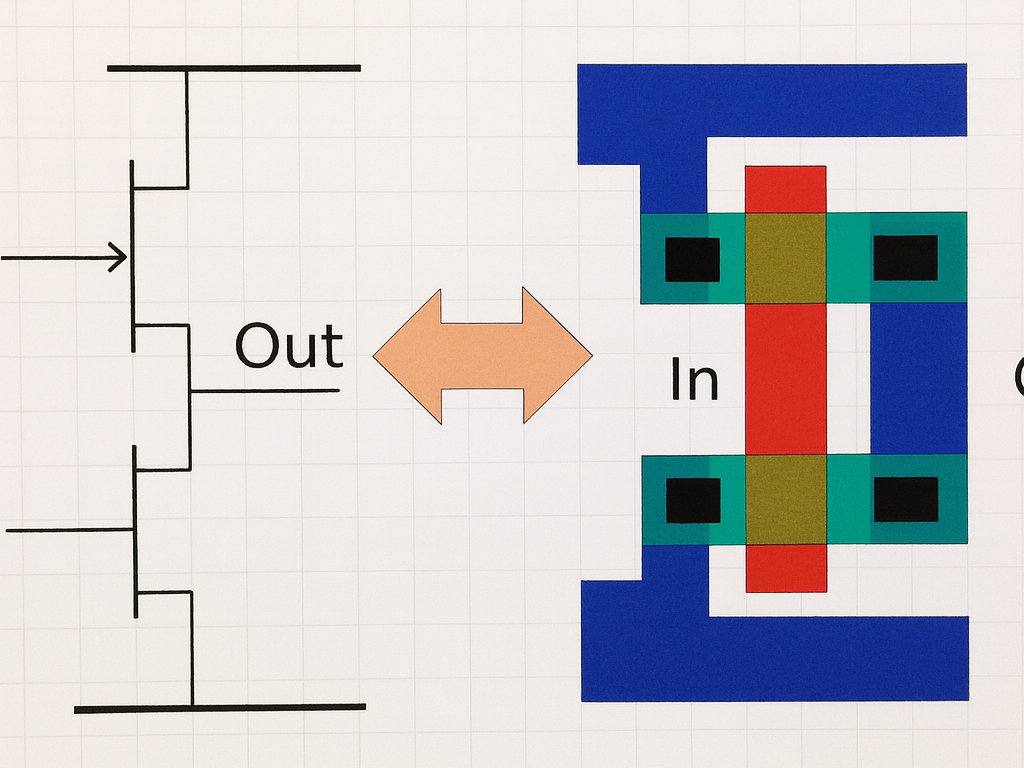

LAYOUT VERSUS SCHEMATIC

電路佈局驗證 LVS

確保佈局的準確性和一致性,幫助設計師確保設計的可靠性和性能。

在集成電路設計中,原理圖是設計師根據電路功能所繪製的圖表,它描述了電路中各個元件(例如電晶體、電阻器、電容器等)之間的連接和相互作用。

驗證流程:

原理圖分析

分析電路原理圖中的元件連接關係

佈局轉換

將原理圖轉換為實際物理佈局

一致性驗證

驗證佈局與原理圖的一致性

可靠性確認

確認設計的可靠性和性能

專業IC設計驗證服務

開始您的IC設計驗證專案

永億資訊提供專業的IC設計驗證服務,包含DRC設計規則檢查和LVS電路佈局驗證,確保您的IC設計符合製造要求,避免晶片故障,提高產品可靠性和成功率。

免費IC設計需求評估

專業DRC和LVS驗證服務

完整驗證報告與建議

立即聯絡我們

填寫諮詢表單,我們將盡快與您聯繫

前往聯絡我們

或加入

LINE@

或來電 04-25680117