DESIGN RULE CHECK

設計規則檢查

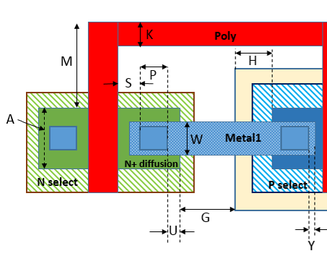

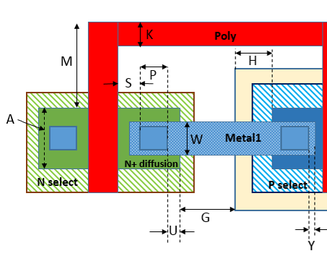

DRC(Design rule checking)是確保設計符合製造要求,並避免芯片故障的重要步驟, 它確保設計與製程技術的限制相符,並有助於提高設計的品質和可靠性。

設計規則檢查(DRC)是一個軟體工具使用製程技術所設定的規則來檢查設計佈局的合規性。 這些規則可以包括晶片元件的間距、尺寸、金屬線寬、接合區域等等。通過進行DRC檢查,設 計師可以確保設計與製造過程的限制相符,並避免可能導致芯片故障或製造問題的設計錯誤。

DRC(Design rule checking)是確保設計符合製造要求,並避免芯片故障的重要步驟, 它確保設計與製程技術的限制相符,並有助於提高設計的品質和可靠性。

設計規則檢查(DRC)是一個軟體工具使用製程技術所設定的規則來檢查設計佈局的合規性。 這些規則可以包括晶片元件的間距、尺寸、金屬線寬、接合區域等等。通過進行DRC檢查,設 計師可以確保設計與製造過程的限制相符,並避免可能導致芯片故障或製造問題的設計錯誤。

LVS(Layout Versus Schematic)驗證確保了佈局的準確性和一致性,幫助設計師確保設計 的可靠性和性能。它也有助於減少後續製程製造的風險,提高產品的可靠性和成功率。

在集成電路設計中,原理圖是設計師根據電路功能所繪製的圖表,它描述了電路中各個元件 (例如電晶體、電阻器、電容器等)之間的連接和相互作用。佈局則是將原理圖中的元件和 連接轉換為實際物理佈局的過程,其中包括元件的位置、佈線的路徑、尺寸等。

FDK(Foundry Design Kit) 用於製造階段,提供設計工程師在實際製造流程中完成設計所需的資源和工具。這半導體製程中的三個重要步驟DRC(Design Rule Checking)、LVS(Layout Versus Schematic)和LPE(Layout Parasitic Extraction)。

DRC (Design Rule Check) 是指對設計按照預定的設計規則進行檢查,以確保設計的合規性。

LVS (Layout Versus Schematic) 是指將佈局與原理圖進行比對,確保它們之間的一致性。